Kurinec, in Encyclopedia of Materials: Science and Technology, 2001 9 Enhancement JFET and MESFET. If the JFET has a lightly doped narrow conducting channel, it is possible to deplete the entire channel at zero gate bias by the built-in potential. On application of a forward bias, a conductive channel can be induced. This is known as the normally off or enhancement mode JFET or E- JFET. Explain why the JFET is so sensitive, and comment on what advantages and disadvantages this gives the JFET as an electronic device. Reveal answer The gate-channel PN junction of a JFET normally operates in reverse-bias mode, whereas bipolar transistors require a forward current for emitter-collector conduction. InterFET has the widest JFET part offerings and is the worlds largest supplier of JFET Products. We have been delivering JFET solutions for over 35 years. A compact and responsive company, we are well positioned to respond to our customers’ special product requirements, to develop marketable new products, and to strengthen and broaden our. Characteristics of JFET Characteristics of JFET: The characteristics of JFET is defined by a plotting a curve between the drain current and drain-source voltage. The variation of drain current with respect to the voltage applied at drain-source terminals keeping the. We offer Ultra-Low-Noise Single and Dual N-CH and P-CH JFETs, High-Speed Lateral Single and Quad DMOS Switches, Ultra-Low-Leakage Current Regulating Diodes, Ultra-Low-Noise Single and Dual N-CH and P-CH Bipolar Transistors and related parts such as Low-Noise Single and Dual Small-Signal MOSFETs, BiFET Amplifiers, Voltage-Controlled Resistors and Photo FETs.

Table of Contents

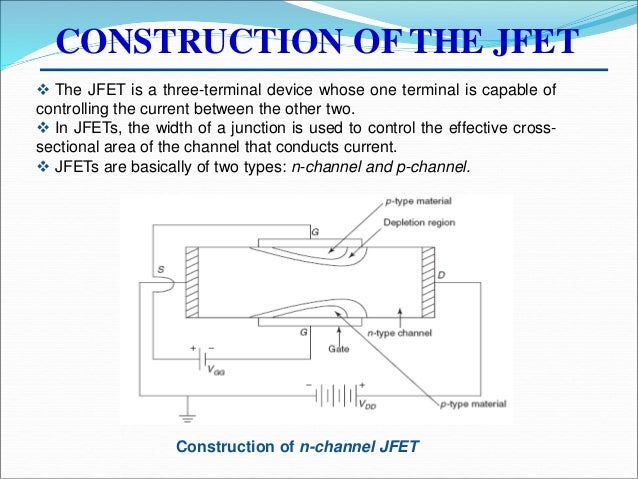

Construction of JFET

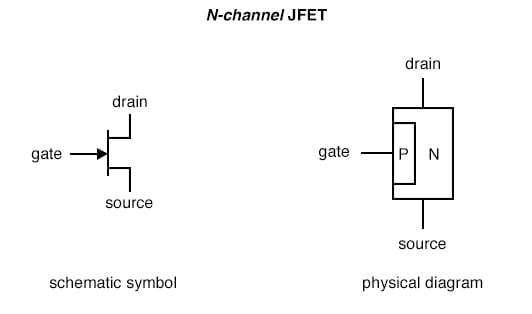

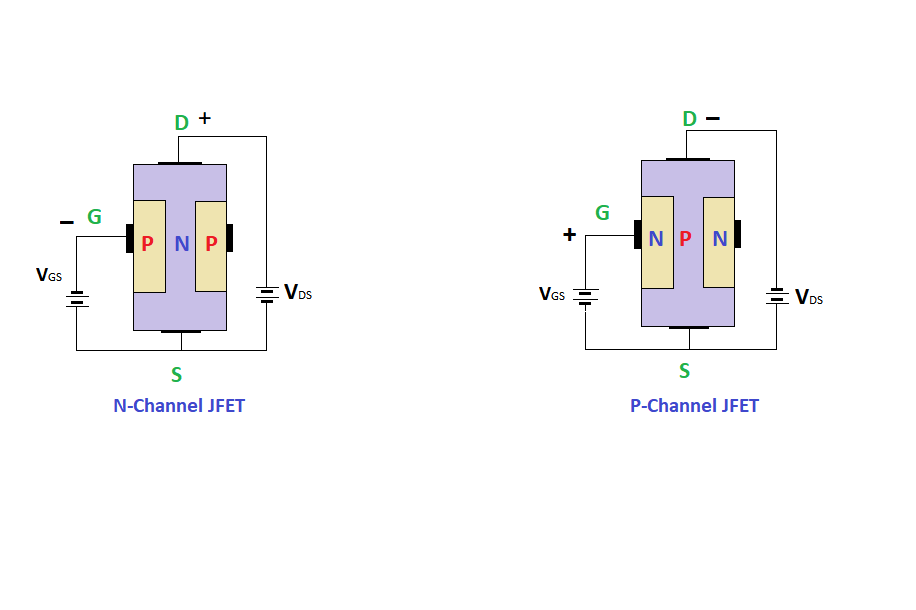

N channel JFET consists of (i) N-type semiconductor bar which forms the channel and (ii) two heavily doped p-type regions formed by diffusion or alloying on two sides of the n-type bar.

n channel JFET shown in the figure. In the case of p channel JFET, the channel is formed by a P-type semiconductor bar and too heavily doped n-type regions are formed on the two sides of the p-type bar forming the channel.

The Jfet Is

In FET, current flows through the channel from the left-hand end (called source) to the right-hand end (called a drain). In the case of N channel FET, the current is carried by electrons ( majority Carriers ) and in the case of p channel FET, the current is carried by holes (majority carriers).

Source

The source S is the terminal ( at the left end of the Bar ) through which the majority carrier enters the bar. The current constituted by the majority carriers entering the bar at S is represented by IS. The electric current IS is taken as positive if it entered the source terminal.

Drain

Drain the drain D is the terminal ( at the right end of the bar ) through which the majority carriers leave the bar. The conventional current entering the channel at drain D is represented by ID.

The electric current ID is taken as positive if it enters the drain current. The drain-to-source voltage is VDS.VDS is positive if the drain D is positive w.r.t he sources. Here VDS = VDD.

Gate

The gate G is formed by two heavily doped p-type regions on the upper and lower sides of the n-type bar. The voltage between the gate and the source is VGS = – VGG is applied to make the PN junction reverse Biased. The electric current entering the gate is represented by IG . The electric current is taken as positive if this current enter the gate.

Channel

The channel of the n-type bar is a portion between to get reasons. The majority of carriers move from the source (S) to the drain (D) through the channel.

Note. The source of JFET corresponds to the emitter of the BJT, gate corresponds to the base of the BJT, and the drain corresponds to the collector of the BJT.

Jfet Current Source

JFETWorking

When a voltage VDS = – VDD is applied between the drain and source terminal but the gate is kept at zero potential, then the depletion layer of PN junction at the side of the bar is established. The region between these two depletion layers is known as the channel. The current carrier electron in n channel flow from source to the drain. The width of the channel determines the flow of current through the channel.

When the reverse voltage VGS = – VGG is applied between the gate and the source terminal, the depletion layer increase in size, and hence the width of the channel decrease. Consequently, the effective conducting cross-section of the channel decreases. As a result of this, the flow of current from the source to the drain decreases.

The flows of current from the source to the train goes on decreasing with the increase in the reverse voltage between the gate and the source. On the other hand, the flow of current from the source to the drain increases when the reverse voltage between the gate and the source decreases.

For a p channel JFET, the current careers in the channel are holes, and the polarities of VGS = – VGG and VDS = – VDD is reversed. The schematic diagram of N channel JFET and p channel JFET is shown in the figure respectively.

The Jfet Is Which Device

Thus the current from the source to the drain can be controlled by the applied voltage ( or electric field ) on the gate. Since the output current ( gate current ) of this type of transistor is controlled by the applied electric field, hence it is known as Field Effect Transistor (FET).

P Channel Jfet

JFET Static Characteristics

The static or common source-drain characteristics of a JFET are the graphical representation of drain current ( ID ) responding to the change in the drain-to-source voltage ( VGS ), when gate-to-source voltage is kept constant.

Set of static characteristics of N channel JFET is shown in the figure.

Discussion of the curves

When VGS = 0 V, the channel between the gate junction is fully open. When VDS = 0, then no electric field is applied and the majority carrier ( electrons ) are not attracted from the source to the drain. Hence the drain current ID = 0.. When the value of VDS increases from zero, then the electric field is set up between drain and source.

Now the current Carriers electrons flow from source to the drain and hence drain current increases linearly. As the value of ID increases, the voltage drop takes place in the bar. This voltage drop reverse biases the gate and hence the width of the channel decreases.

The narrowing of the channel is not uniform as the voltage drop takes place along the length of the channel. The width of the channel goes on decreasing as we move away from the source. Ultimately a critical value of VDS is reached when the channel is pinched off as shown in the figure.

This value of voltage VDS is known as pinch-off voltage VP. At this voltage, the value of the gate current ID also becomes constant.

However, the channel is not completely blocked. If the channel is completely blocked at the Pinch off voltage, then ID would have been reduced to zero.

As the value of VDS increases, the reverse voltage between the channel and the gate becomes, hence the breakdown of the gate junction takes place, resulting into a sharp increase in the drain current.

When VGS is negative, the reverse bias between the channel and the gate increases. As a result of this, the resistance of the channel increases, the drain current decreases. The Pinch Of takes place at a lower value of VDS . Similarly, the break down of the gate junction also takes place at lower value of VDS.

The Jfet Is Important

Since that gate current is controlled by the gate bias beyond Pinch off, so the amplification of the signal can be achieved by changing the gate bias.